JPB2 JPA JPA JPB2 JP B2 JP B2 JP B2 JP A JP A JP A JP A JP A JP A JP B2 JP B2 JP B2 Authority JP Japan Prior art keywords overflow numerical sign addend result Prior art date Legal status (The legal status is an · Verilogで正数同士の乗算器 verilogHDL FPGA で設計をしていると乗算器などは自分で書くよりもIPに任せた方が早かったりします。 (私のコードが悪いだけか?) そこで正数同士の乗算器の作り方を勉強のためメモしておきます。 4bit同士 (a,b)のかけ算は以下のよう · 基本情報でわかる 論理演算 「真理値表を書けば、半加算器と全加算器の仕組みがわかる」 矢沢 久雄 1117 更新 この連載では、基本情報技術者試験によく出題されるテクノロジー関連の用語を、午前問題と午後問題のセットを使って解説します。 午前

Test04 回路を部品化する にがてぶろぐ

4bit加算器 verilog

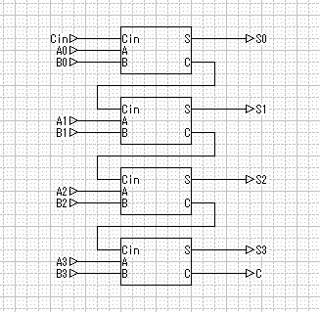

4bit加算器 verilog-次に、半加算器と全加算器を用いて、4bitの加算回路を設計しましょう。 ソースコードの例を、以下に示します。 ここで、4bitの入力A、BをそれぞれA(3)、A(2)、A(1)、A(0)、そして、B(3)、B(2)、B(1)、B(0) のように表しています。 また、それらの和に対応する 5bit の出力をS(4)、S(3)、S(2)、S(1)、S(0)としています。 それらを定義するport 文では、std_logic_vector(3 downto 0/12/ · VHDLで4ビット加算器を作る / ライブラリーを使う 動かしてわかるCPUの作り方10講 pp 今度はライブラリーを使って4ビット加算器を作ってみる。 ただの足し算で表現できる。 5LEを消費した。 library IEEE;

1999 号 乗算器 Astamuse

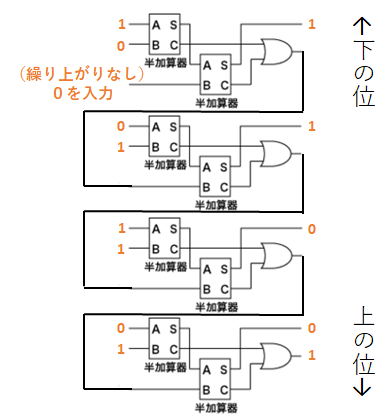

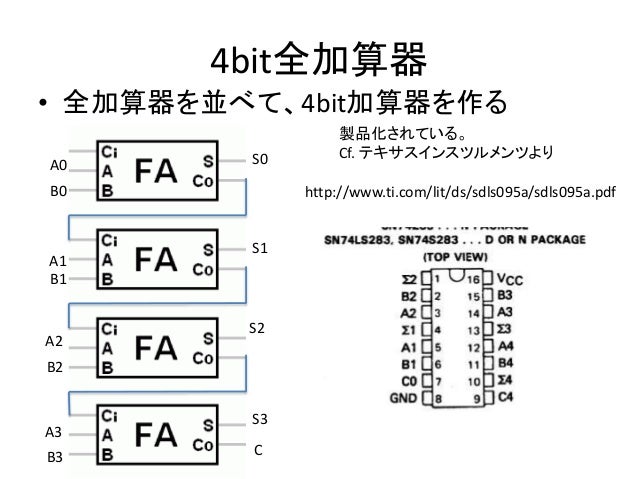

4bit加算器 いかに4bitの加減算回路を作成し、計算結果の3bit目と4bit目のXORを取得しオーバーフローフラグを確認してみました。 7(0111) 1(0001) = 8(1000) 桁あふれ 8(1000) – 1(0001) = 9(0111) 桁あふれ8(1000) 7(0111) = 1(1111) 桁あふれ無し · 4bit加算器の例(0101 1110 = ) 上の回路を4つ接続することによって、4bitの加算器を作ることができる(下図)。 この回路では、下にある加算器がより上位の桁の計算を行うため、入出力は下から上に読むことになる。そのため0101の入力は、各半加算器1のA端子に上から1, 0, 1, 0を入力する。同様に、1110は各半加算器2のB端子に上から0, 1, 1, 1を入力する。 各全加算About Press Copyright Contact us Creators Advertise Developers Terms Privacy Policy & Safety How works Test new features Press Copyright Contact us Creators

加算器(かさんき、Adder)とは、加算を行う演算装置である。 この記事ではデジタル回路によるものについて説明する。 アナログ回路による加算回路の一例はオペアンプ#加算回路(電圧によるもの。 他に電流の加算もある)を参照。加算器 x1 x0 ci s3 s2 co fa4 x3 x2 y1 y0 y3 y2 s1 s0 fa x y co ci s fa x y co ci s fa x y co ci s fa x y co ci s x y co s fa ci 減算 除数を2 の補数に変換してから加算 x の2 の補数 2nx 例 5 (0101) の2 の補数(4ビット) 165 = 11(1011) ①全てのビットを反転させる ②1 を加える 0101 1010 1011 ① ②全加算器の二次元配列を用いた乗算器 回路規模・消費電力・演算時間が大 部分積&加算のため全加算器の2次元配列 例:8bit×8bit の場合 直接的構成では8×8=64個の全加算器が必要

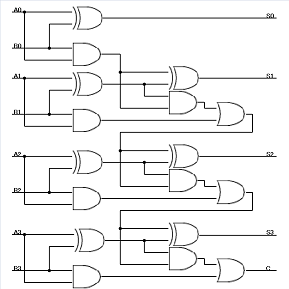

· 221 ステップ1 半加算器の回路図から始める; · 電子回路ドリル II(9) MONOist 問題9 ゲート回路の簡単化 : 完全マスター! 電子回路ドリル II(9) » 08年03月13日 00時00分 公開 横田 · 4bitの全減算器の真理値表はどのようになりますでしょうか。 そもそも4bitとは何を表しているのでしょうか。 真理値表を聞く前に、基礎???をやりなさい。

Cpuの創りかた 7 加算器を作る Qiita

1999 号 桁上げ先見回路および並列加算器 Astamuse

· CPUはマイコンの中枢ですが、さらにその中で演算を行うユニットがALU(Arithmetic and Logic Unit)です。マイコンの核に相当するといってもよいでしょう。実際の算術演算、論理演算はALUで行われます。今回は、ALUの中身がどうなっているかを説明します。 (2/4)1 C0= A·B B·C1 C1·A S = A·B·C A·B·C A·B·C A·B·C = A·(B·C B·C) A·(B·C B·C) = A·(B⊕C) A·(B⊕C) = A⊕(B⊕C) = A⊕B⊕C 加算回路 · 備忘録②の続き。 加算回路 半加算器 2進数の足し算は、 0 0 = 0 0 1 = 1 1 0 = 1 1 1 = 10 と書ける。これの足される数を入力a、足す数を入力b、その桁の加算結果を出力s、桁上りを出力coとして真理値表で示すと、以下のようになる。coは桁上りが生じたかどうかを表すビットであ

Cpuよもやま話 論理ゲートを使って加算器を作ってみよう Vbaの勉強を始めてみた

にがてぶろぐ

6 アドレス復号化器(address decoder) – 入力 n ビット信号D =(Dn1,,D0) – 出力 2n本の1ビット信号Q =(Q 2n1,Q0) ただし、1本のみ1,残りの2n1本は0 が出力される D2 D1 D0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 アドレスデコーダ D QDQ 000 100 001 101X = 0 のとき(加算) b i ⊕0 = b i なので(b3,b2,b1,b0) はそのまま全加算器のb 入力に入る 桁上げの初期値c0 はx = 0 ⇒ 下記の回路(加算回路) と等価になる FA co s a b ci FA co s a b ci FA co s a b ci FA co s a b ci a3 b3 a2 b2 a1 b1 a0 b0 c4 s3 s2 s1 s0 c3 c2 c1 c0=0 x = 1 のとき(減算) b i ⊕1 = b · 4ビット加算器は全加算器(full adder)と半加算器(half adder)を組み合わせることによって作成することができます。まずは、今回使用した半加算器と全加算器を見ていきましょう。

問題9 ゲート回路の簡単化 完全マスター 電子回路ドリル Ii 9 Monoist

4ビット同士の加算回路をmil記号を用いて図示せよ という問題はどういう考 Yahoo 知恵袋

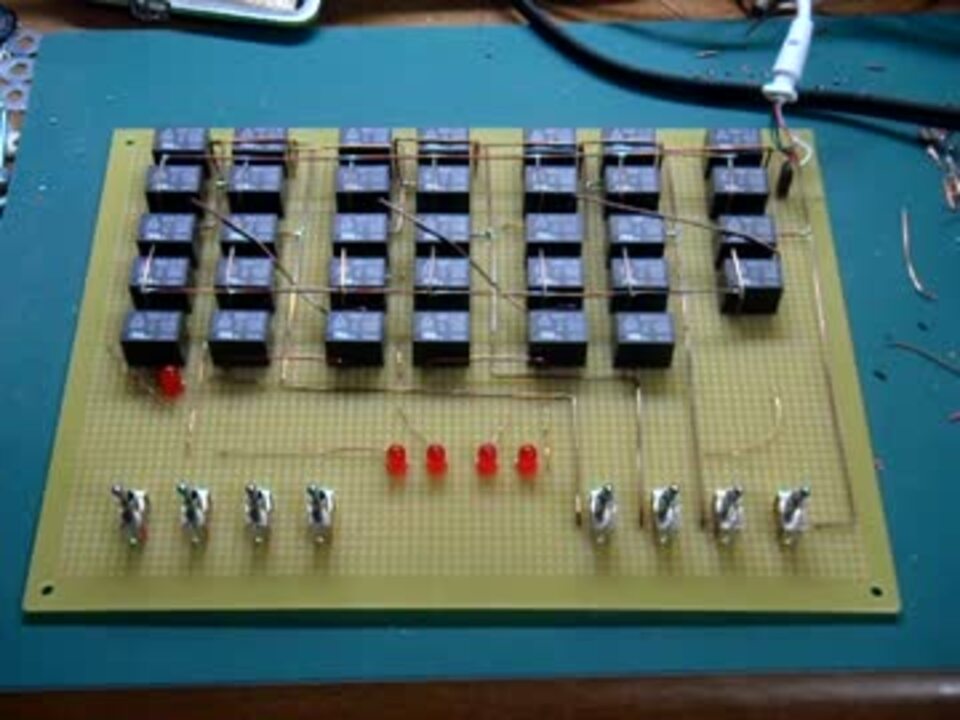

半加算器やリレーによる半加算器のページで、 基本論理回路やリレーを使えば、 半加算器を作れることが分かりました。 半加算器は 2 個の 2 進数の足し算ができます。 0 + 1 = 1、 1 + 1 = 10 などが計算できる 「賢い」 回路です。5 計算機論理設計AMatsuzawa 2 5 加算器 05年11月10日1 桁目に半加算回路(ha)、2 桁目以上に全加算回路(fa)を使用することで構成する ことができる。 たとえば、a3a2a1a0 b3b2b1b0 = cs3s2s1s0 を計算する4 ビットの加算回路は、 下図のようになる。 4 ビット加算回路 ha a b s c a fa b s c co a fa b s c co a fa b s c co ao bo a1 b1 a2 b2 a3 b3 so s1 s2 s3 c

リレーによる 4bit 加算回路

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

· 半加算器 Half adder Logisimは、作った回路を部品として使えるので、上記半加算器にHAというラベルを付けて、それを元に1bitの全加算器を作りました。 全加算器 Full adder 最後に、1bitの全加算器を4つ繋げて4bitの加算器を作りました。 最下位ビットはは半加算器を使う方法と全加算器を使う方法があるようです。 4bit 加算器 4bit adderUsigned数を演算するためのlibraryを使う。 entity adder_4bit_lib is port( AIN in全加算器、半加算器を組み合わせると複数桁加算器を構成することができる。 例として、下記のような 4 桁の 2 進数の加算を行なう回路を示す。 1011 各桁を左から A1 とする, =1, A3=0, =1, A1=1 1101 各桁を左から B4 B1 とする, B4=1, =1, B2=0, B1=1

Vhdlで4ビット加算器を作る 全ビットを全加算器にしてみる

全加算器 N Bit加算器 Ushitora Lab

· miyanetdev 19年4月26日 / 19年4月29日 みなさんこんにちは! 今回はVerilogHDLというハードウェア記述言語を使って、nビット加算器を作っていきたいと思います。 nビット加算器を作るために利用した半加算器や全加算器についての説明していくので 論理回路 · 半加算器 や スイッチ(リレー)による半加算器 のページで、基本論理回路やリレーを使って半加算器を作れることが分かりました。 半加算器は 2 進数の 1 桁の足し算ができます。 しかし、2 進数の 1 桁だけでは、これが本当に使い物になるのか、少し気懸かりです。 · この加算器はFull Adderと呼ばれ、FAと略して記載します。 4bit加算器 半加算器と全加算器を組み合わせると桁が多くなっても計算することが出来ます。具体例として59の結果を示します。 減算器 減算器は加算器で表現することが出来ます。

Test04 回路を部品化する にがてぶろぐ

番外編 chap 5 ラダー図で加算器をつくる 2

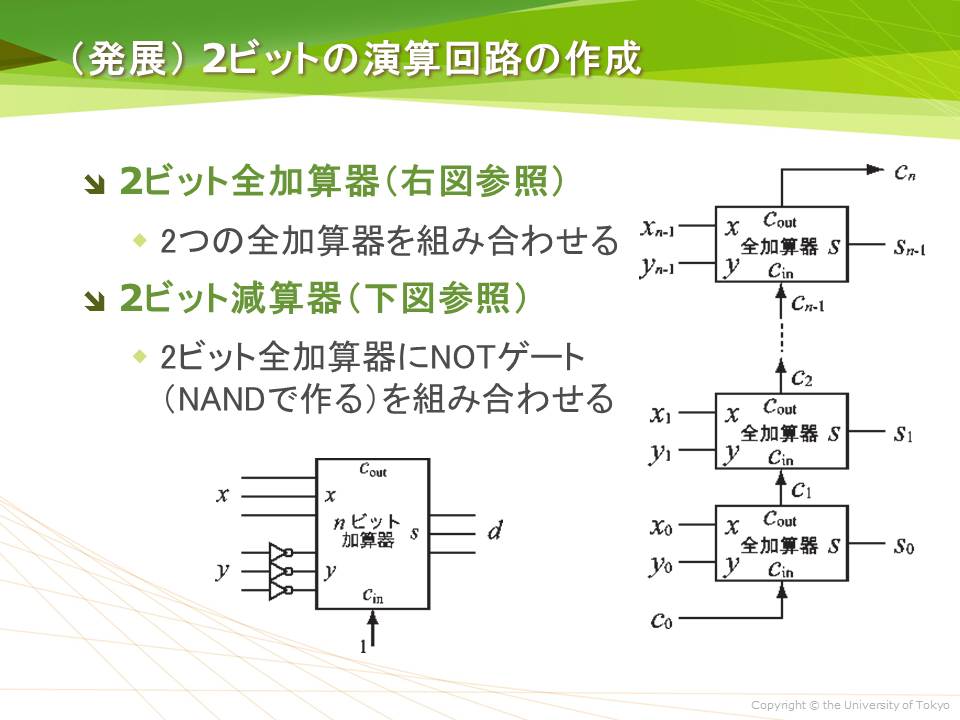

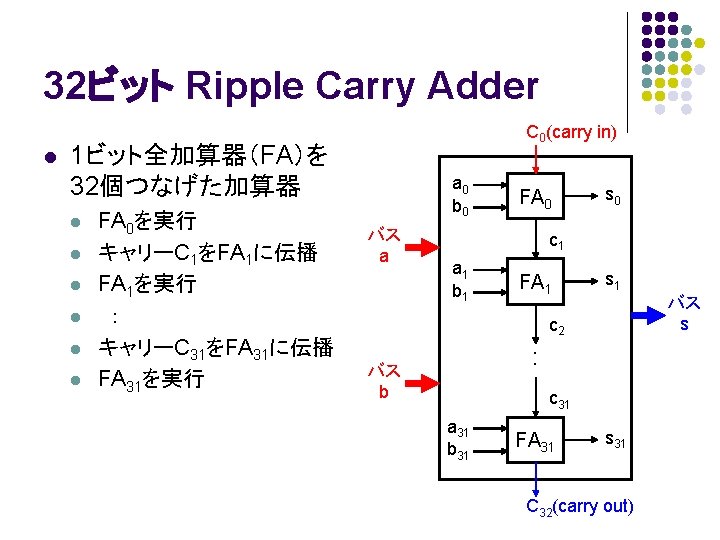

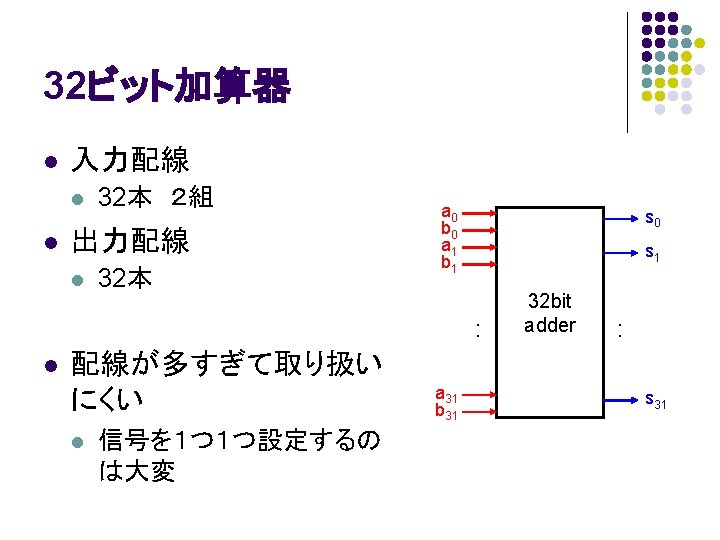

第2回 加算器(その1) 半加算器と全加算器(p52~) コンピュータは演算を行うもの、で、すべての演算は加算から導かれますから、 加算を行う加算器 (adder)は、まさにコンピュータの基本要素といえます。そして2進数で数値・データをあらわす現在のコンピュータでは、 2進数の加算を行う加算器32ビット加算器の設計 1ビット加算器を使った32ビット加算器 s31 a31 cout s1 s0 b31 b1 b0 a1 a0 cout cout cin 0 cin 下位から上位へ桁上げが伝播 ・・・ cout cin 順次桁上げ加算器減算器は加算器を用いてどうつくるか? • abなる引き算はaとbの2の補数の加算であった。 (思い出すべ し!!!!) • したがって、2の補数器と加算器で減算器が作れる。 • 2の補数=1の補数+1であった。 (思い出すべし!!!!) • 1の補数は各桁を反転したもの

4 演算回路の作成

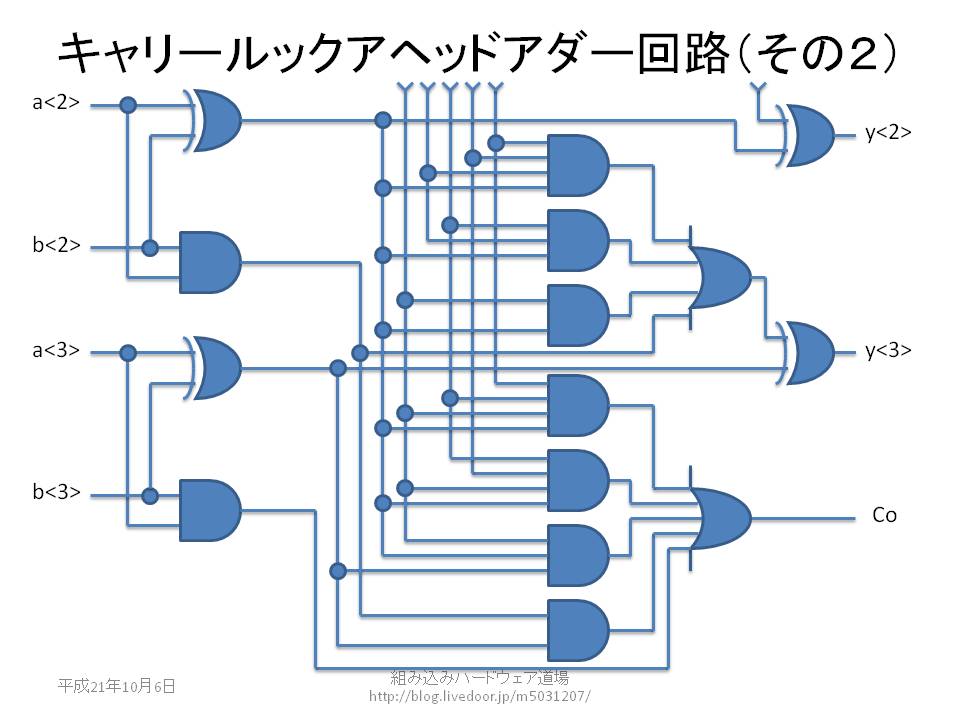

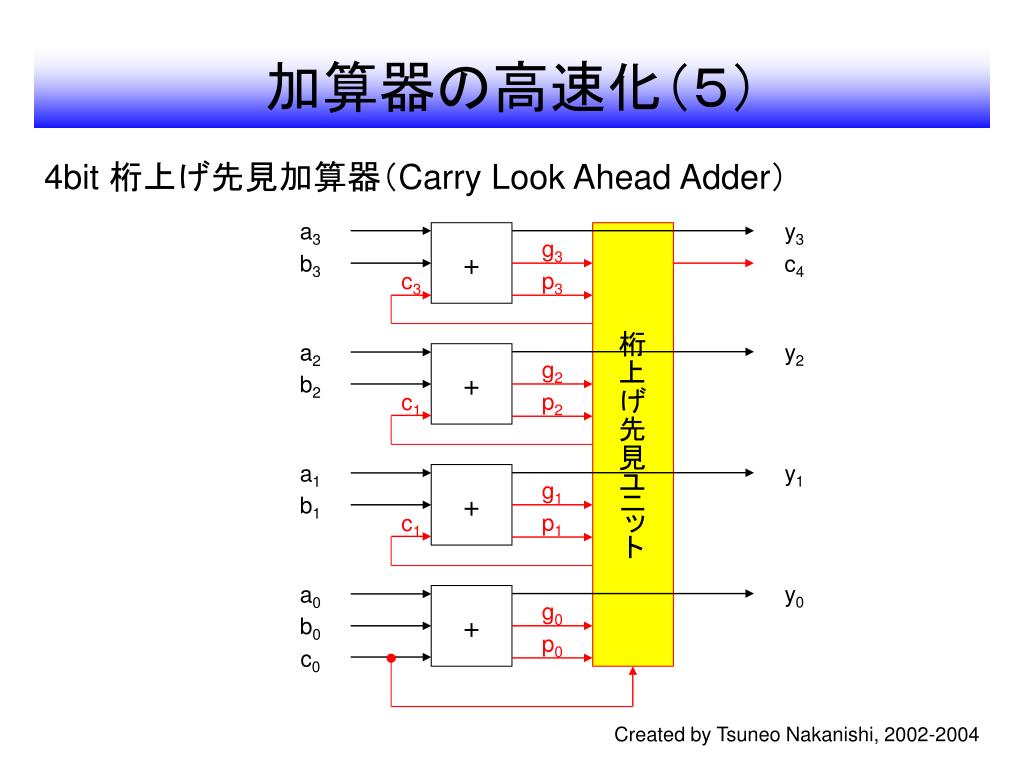

キャリールックアヘッドアダー回路 組み込みハードウェア道場

Created Date 4/25/07 PM図7に基づいて作成した4ビット乗算器 Verilog 記述例を以下に示す。 モジュール ADDER4 は課題1で作成した4ビット加算器である。 また、モジュール MULTIPLIER4X1 は図6に示す ABi を求める回路で4bit全加算器 OxygenNotIncluded Advanced Notes 4bit全加算器 #OxygenNotIncluded学会 #ONI計算機科学 1515までは計算できます デジタル回路における 加算器 とは、2つのデジタル信号を足した結果を計算する回路の事を言う AutomationPack以前からも加算器自体は作れた

直列加算器の動作 シフトレジスタのmodeを load にします modeをloadにすると シフトレジスタはパラレル入力となり load clk a bでデータをloadします dip sw data a data bに計算する値を

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

· 以下全て4bitで考えます。最初に見た 0011 ) 1101 を考えます。これを符号付き整数同士の加算と考えると という正しい計算ですが、符号なし整数同士の加算と考えると という間違った計算になります。コンピュータから見ればどちらも正当な2進数の操作ですが、人間から見ると全く違う結果になります。/12/ · vhdlで4ビット加算器を作る / 全ビットを全加算器にしてみる 動かしてわかるCPUの作り方10講 前回はテキストどおりにビット0だけを半加算器にしたが、今度は全ビットを全加算器にしてみ

論理回路シミュレータlogisimで加算回路 はじめてプログラム

4ビット全加算器 水玉製作所

Ppt 算術論理演算ユニットの設計 Powerpoint Presentation Free Download Id

4bit 3bitの乗算回路をリプルキャリ型の5bit加算器二つと いくつ Yahoo 知恵袋

File 4 Bit Carry Lookahead Adder Svg Wikimedia Commons

4bit 全加算器 Cmos Dip16 Cd74hc2e Texas Instruments製 電子部品 半導体通販のマルツ

4bit全加算器 Oxygennotincluded Advanced Notes

Experiment 実験 組み合わせ回路と順序回路を体験するため 以下の2つの回路を組みました 当日は実際に回路を展示します 加算回路加算回路は組み合わせ回路の簡単な例です 今回は 全加算器を4つ用いて4bit 4bitの加算回路を組みました 実際に

全加算器を利用した4ビットの加算回路の回路図が分からないので Yahoo 知恵袋

Test04 回路を部品化する にがてぶろぐ

加算器

アーキテクチャ 4bit積算回路の設計方法 Teratail

加算器 その1 Kivantium活動日記

加算器 減算器の原理 制御工学の基礎あれこれ

リレーによる 4bit 加算回路

4bit全加算器 Oxygennotincluded Advanced Notes

リレーによる 4bit 加算機

減算回路 ヘキサドライブ日記

4ビット全加算器 水玉製作所

リレーでつくる4ビット2進加算器

リレー式 4bit加算器 ニコニコ動画

シンクロナイザ 非同期入力の同期化

Bus Public Class Bus Path Paths N Public

問題2 4ビット加算器をverilog Hdlで記述しよう 完全マスター 電子回路ドリル Iii 2 Monoist

Http Www Ed Noda Tus Ac Jp Jte401 Files 19 Text 2 Pdf

組合せ回路の例 加算回路

にがてぶろぐ

量子コンピュータで量子化学のfullciが超高速になる かも

Chap9

加算器 減算器の原理 制御工学の基礎あれこれ

4bit加算器 株式会社ヘキサドライブ Hexadrive ゲーム制作を中心としたコンテンツクリエイト会社

組合せ回路の例 加算回路

4 N桁の加算

リレーによる半加算器

Ltspice 全加算器を作成する Miraiportal

問題9 ゲート回路の簡単化 完全マスター 電子回路ドリル Ii 9 Monoist

Bus Public Class Bus Path Paths N Public

半加算器及び全加算器を用いて 4bit二進数のaとbに対し A Yahoo 知恵袋

4bit加算器 ヘキサドライブ日記

加算器 減算器の原理 制御工学の基礎あれこれ

Wiiマリオで4bit加算器を作ってみた 計算速度最速 ニコニコ動画

第2回

半加算器及び全加算器を用いて 4bit二進数のaとbに対し A Yahoo 知恵袋

4bit加算器 2 写真共有サイト フォト蔵

Http Www Ed Noda Tus Ac Jp Jte401 Files 19 Text 2 Pdf

加法器 维基百科 自由的百科全书

Cpuよもやま話 論理ゲートを使って加算器を作ってみよう Vbaの勉強を始めてみた

リレー式 4bit加算器 Youtube

論理ゲートをpythonで作ってcpuを学ぶ 第1回 Qiita

情報画像工学実験ii 実験6 論理回路設計

リレーを使った4ビット2進加算器 Gijyutu Com 技術の面白教材集

第2回

Fpga入門 備忘録 組み合わせ回路編 ハードウェアエンジニアの備忘録

1997 号 論理演算回路及びキャリールックアヘッド加算器 Astamuse

トラ技 年 5 月号に感化されて 4 Bit コンピュータを Mos Fet で製作する Qiita

Test04 回路を部品化する にがてぶろぐ

加算器 減算器の原理 制御工学の基礎あれこれ

4ビット全加算器 水玉製作所

乗算器 その1 Hackmd

Http Www Ed Noda Tus Ac Jp Jte401 Files 19 Text 2 Pdf

リレーでつくる4ビット2進加算器

先ほどの1bit全加算器を4個つなげると 4bit全加算器 Weed Flickr

レジスタ セレクタ にalu 4bit全加算器 をつなげた Weed Flickr

Http Www Ed Noda Tus Ac Jp Jte401 Files 19 Text 2 Pdf

1999 号 乗算器 Astamuse

論理ゲートをpythonで作ってcpuを学ぶ 第1回 Qiita

除算回路 ヘキサドライブ日記

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

組合せ回路の例 加算回路

リレーによる 4bit 加算機

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

リレーによる 4bit 加算回路

ハードウェア記述言語 その2

リレーによる半加算器

3ビットの加算器の構造図を半加算器と全加算器を用いて図示してください Yahoo 知恵袋

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

問題2 4ビット加算器をverilog Hdlで記述しよう 完全マスター 電子回路ドリル Iii 2 Monoist

加算器

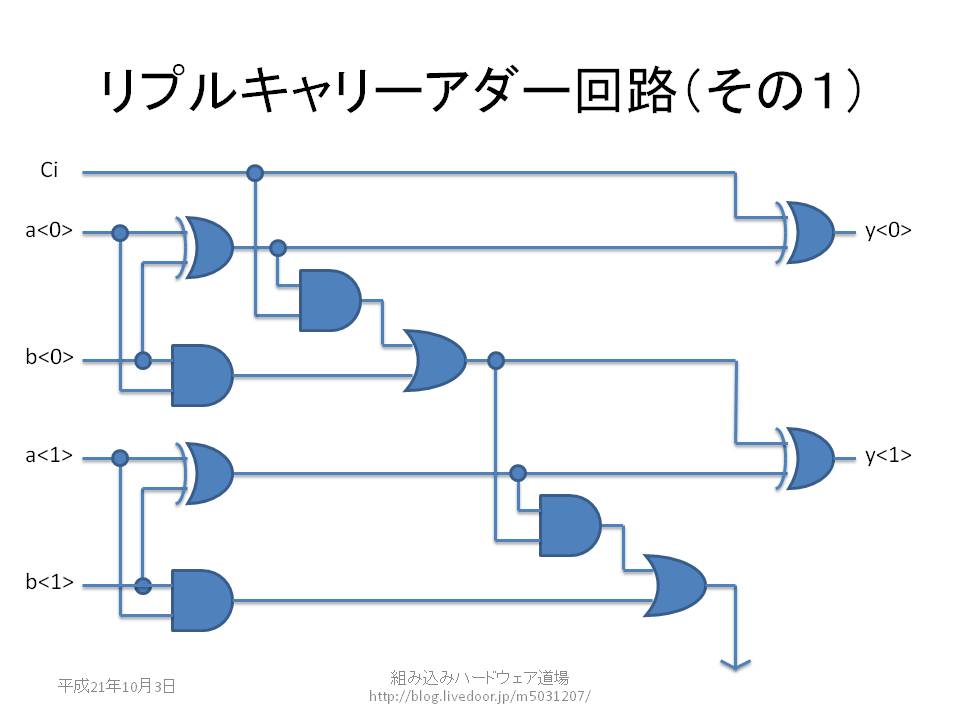

リプルキャリーアダー回路 組み込みハードウェア道場

Fpga入門 正誤表

減算回路 ヘキサドライブ日記

Logisim 全加算器で4bit足し算 Youtube

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

ハードウェア記述言語 その2

0 件のコメント:

コメントを投稿